Rev. V2

#### **Features**

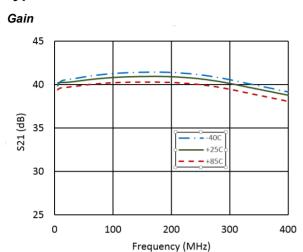

- 40 dB Gain

- 15.5 dB, 0.5 dB steps, 5 Bit Digital Step Attenuator

- 36 dB MER, 64 QAM 39 Channels, 52 dBmV/ch.

- 8 V Operation

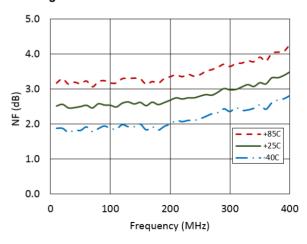

- 2.6 dB Noise Figure

- Serial or Parallel Attenuator Control

- Differential Input and Output

- Low Harmonics

- Power Down Mode

- Lead-Free 7 mm 48-lead PQFN Package

- Halogen-Free "Green" Mold Compound

- RoHS\* Compliant

### **Description**

The MAAM-011168 is an integrated 2 stage differential amplifier with embedded digital step attenuator (DSA) assembled in a lead-free 7 mm 48-lead PQFN package.

The module provides excellent linearity and high output power with greater than 30 dB MER for 64 QAM modulation with 39 channels and 52 dBmV per channel. Gain in the minimum attenuation state is typically 40 dB. The internal DSA offers 15.5 dB attenuation range with 0.5 dB steps. The device is optimized for high output power with 8 V bias and can also operate from 5 V bias if lower DC power consumption and output level is desired. The module also provides a power down function for each of the amplifier stages.

This amplifier is ideally suited for use in CATV reverse path applications.

### Ordering Information<sup>1,2</sup>

| Part Number        | Package           |

|--------------------|-------------------|

| MAAM-011168-TR1000 | 1000 piece reel   |

| MAAM-011168-TR3000 | 3000 piece reel   |

| MAAM-011168-001SMB | Sample Test Board |

- 1. Reference Application Note M513 for reel size information.

- 2. All sample boards include 5 loose parts.

- \* Restrictions on Hazardous Substances, European Union Directive 2011/65/EU.

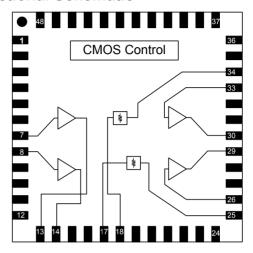

#### **Functional Schematic**

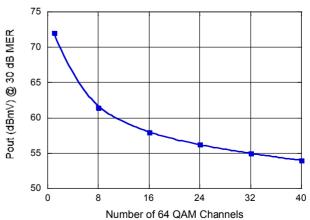

### Pin Configuration<sup>3</sup>

|            | _                     |            |                                  |

|------------|-----------------------|------------|----------------------------------|

| Pin<br>No. | Description           | Pin<br>No. | Description                      |

| 1          | Latch Enable          | 30         | Stage 2 Output (+)               |

| 6          | Stage1 Feedback (+)   | 32         | Stage 2 Feedback(+)              |

| 7          | Stage 1 input (+)     | 33         | Stage 2 Input (+)                |

| 8          | Stage 1 input (-)     | 34         | Attenuator Output (+)            |

| 9          | Stage 1 Feedback(-)   | 36         | DSA Serial Output                |

| 13         | Stage 1 Output (+)    | 37         | Power Up Select 2                |

| 14         | Stage 1 Output (-)    | 38         | Power Up Select 1                |

| 15         | Enable Stage 1        | 39         | V <sub>DD</sub> CMOS Controller  |

| 16         | Stage 1 Bias Voltage  | 40         | Unused Control (B5) <sup>5</sup> |

| 17         | Attenuator Input (-)  | 41         | Attenuator Bit 4 (8 dB)          |

| 18         | Attenuator Input (+)  | 42         | Attenuator Bit 3 (4 dB)          |

| 20         | Stage 2 Bias Voltage  | 43         | Attenuator Bit 2 (2 dB)          |

| 21         | Enable Stage 2        | 44         | Attenuator Bit 1 (1 dB)          |

| 25         | Attenuator Output (-) | 45         | Attenuator Bit 0 (0.5 dB)        |

| 26         | Stage 2 Input (-)     | 46         | Parallel/Serial Select           |

| 27         | Stage 2 Feedback(-)   | 47         | Clock                            |

| 29         | Stage 2 Output (-)    | 48         | Serial Input                     |

|            |                       | 49         | RF and DC Ground <sup>4</sup>    |

|            |                       |            |                                  |

- All pins not listed in the table are "No Connection" and should be left unconnected.

- The exposed pad centered on the package bottom must be connected to RF and DC ground.

- MACOM recommends grounding pin 40. It is connected to the CMOS controller but does not affect attenuator setting.

# Differential CATV Variable Gain Amplifier 5 - 300 MHz

Rev. V2

## Electrical Specifications: $T_A$ = +25°C, $V_{CC}$ = 8 V, minimum attenuation state, $Z_0$ = 75 $\Omega$

| Parameter                                    | Test Conditions                                                                                                                                                        | Units | Min.           | Тур.                 | Max. |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|----------------------|------|

| Gain                                         | Max. Gain State @ 100 MHz, -29 dBm P <sub>IN</sub>                                                                                                                     | dB    | 38             | 40                   | 42   |

| Gain Slope                                   | Positive tilt from 5 - 200 MHz                                                                                                                                         | dB    | _              | 1.0                  |      |

| Noise Figure <sup>6</sup>                    | _                                                                                                                                                                      | dB    | _              | 2.6                  | _    |

| Input Return Loss                            | _                                                                                                                                                                      | dB    | _              | 22                   | _    |

| Output Return Loss                           | _                                                                                                                                                                      | dB    | _              | 22                   | _    |

| Reverse Isolation                            | _                                                                                                                                                                      | dB    | _              | 50                   | _    |

| Attenuation Range                            | 100 MHz, Relative to maximum gain, -29 dBm P <sub>IN</sub>                                                                                                             | dB    | 14.6           | 15.5                 | 16.4 |

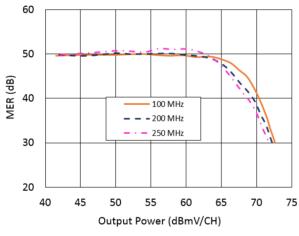

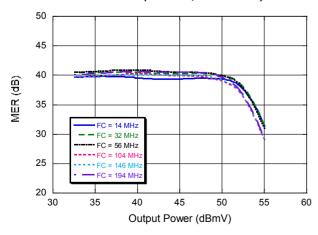

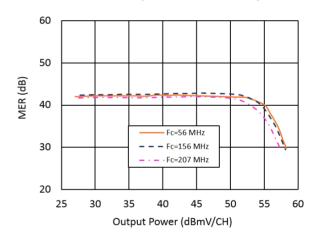

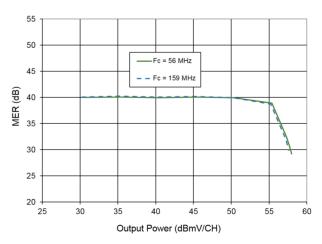

| 64 QAM<br>Modulated Error Ratio <sup>7</sup> | 39 Channels (5 - 250 MHz), 51 dBmV/Ch.<br>Single Channel (8 - 200 MHz), 71 dBmV/Ch.<br>Single Channel (250 MHz), 70 dBmV/Ch.<br>16 Channels (5 - 250 MHz), 56 dBmV/Ch. | dB    | <br><br><br>30 | 36<br>35<br>35<br>34 | _    |

| P1dB                                         | _                                                                                                                                                                      |       | _              | 27                   |      |

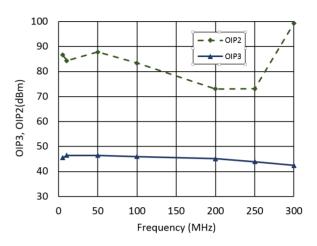

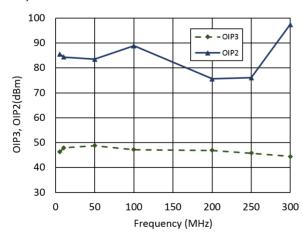

| OIP2                                         | 2-tone,+9 dBm/tone, 1 MHz tone spacing, 200 MHz                                                                                                                        | dBm   | _              | 74                   | _    |

| OIP3                                         | 2-tone,+9 dBm/tone, 1 MHz tone spacing, 200 MHz                                                                                                                        | dBm   | _              | 44                   | _    |

| T <sub>ON</sub> , T <sub>OFF</sub>           | 50% Control to 90 / 10 % RF                                                                                                                                            | ns    | _              | 400                  | _    |

| Icc                                          | EN1 = EN2 = 5 V                                                                                                                                                        | mA    | _              | 290                  | 315  |

| I <sub>CC_OFF</sub>                          | EN1 = EN2 = 0 V                                                                                                                                                        | mA    | _              | 3                    | 10   |

| I <sub>EN1</sub> , I <sub>EN2</sub>          | EN1 = EN2 = 5 V                                                                                                                                                        | mA    | _              | 0.7                  |      |

<sup>6.</sup> Includes Balun loss

<sup>7.</sup> Modulation error ratio each channel 64 QAM 5.12 MS/s

Rev. V2

## Absolute Maximum Ratings<sup>8,9,10</sup>

| Parameter                          | Absolute Maximum |

|------------------------------------|------------------|

| RF Input Power                     | -8 dBm           |

| Bias Voltage (V <sub>CC</sub> )    | 10 V             |

| Control Voltage                    | -0.5 V to 5.5 V  |

| Operating Temperature              | -40°C to +100°C  |

| Junction Temperature <sup>11</sup> | +150°C           |

| Storage Temperature                | -65°C to +150°C  |

- 8. Exceeding any one or combination of these limits may cause permanent damage to this device.

- MACOM does not recommend sustained operation near these survivability limits.

- 10. Operating at nominal conditions with  $T_J \le 150^{\circ} C$  will ensure MTTF > 1 x  $10^6$  hours.

- 11. Junction Temperature  $(T_J) = T_C + \Theta jc * (V * I)$ Typical thermal resistance  $(\Theta jc) = 8.85^{\circ}$  CW.

a) For  $T_C = +25^{\circ}C$ ,

T<sub>J</sub> = 47°C @ 8 V, 315 mA

b) For  $T_C = +100$ °C,

$T_J = 122^{\circ}C @ 8 V, 315 mA$

### Truth Table 12

| В5 | В4 | ВЗ | B2 | B1 | В0 | Attenuation (dB) |

|----|----|----|----|----|----|------------------|

| Х  | 1  | 1  | 1  | 1  | 1  | Minimum          |

| Х  | 1  | 1  | 1  | 1  | 0  | 0.5              |

| Х  | 1  | 1  | 1  | 0  | 1  | 1                |

| Х  | 1  | 1  | 0  | 1  | 1  | 2                |

| Х  | 1  | 0  | 1  | 1  | 1  | 4                |

| Х  | 0  | 1  | 1  | 1  | 1  | 8                |

| Х  | 0  | 0  | 0  | 0  | 0  | 15.5             |

12. Logic "0" = 0 V to  $0.8 \text{ V} \pm 0.2 \text{ V}$ , Logic "1" = 2 V to  $5 \text{ V} \pm 0.2 \text{ V}$ .

Rev. V2

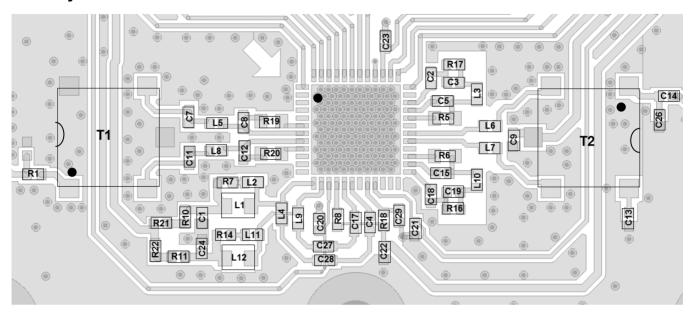

### **PCB** Layout

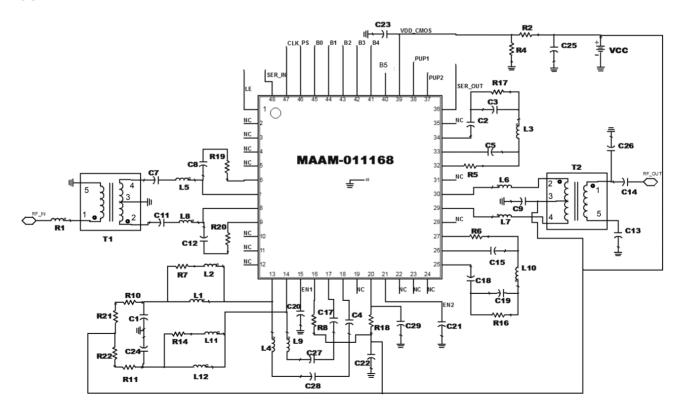

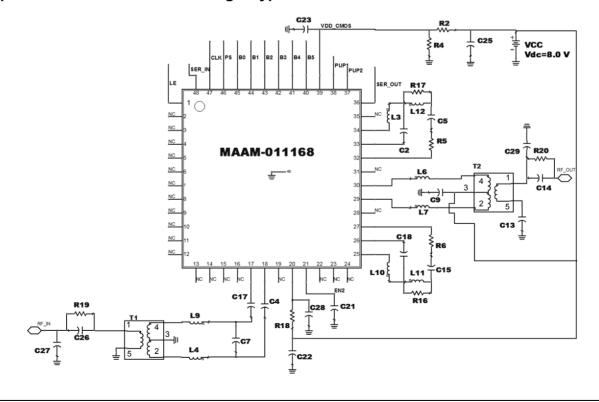

### **Application Schematic**

# Differential CATV Variable Gain Amplifier 5 - 300 MHz

Rev. V2

### Parts List: 8 V Application circuit

| 0.1 µF  | Case Style 0402                                                                         | Function/Notes                                                                                                                                                                              |  |

|---------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| •       | 0402                                                                                    | DE Dynasa                                                                                                                                                                                   |  |

| 0.1 uF  |                                                                                         | RF Bypass                                                                                                                                                                                   |  |

| υ. ι μι | 0402                                                                                    | DC Block                                                                                                                                                                                    |  |

| 150 pF  | 0402                                                                                    | Gain Tilt (with R16 and R17)                                                                                                                                                                |  |

| 1 μF    | 0805                                                                                    | Low Frequency Bypass                                                                                                                                                                        |  |

| 1 pF    | 0402                                                                                    | Output Match                                                                                                                                                                                |  |

| 47 μH   | 0806                                                                                    | V <sub>C</sub> C1 Choke. Murata LQH2MCN470K02L                                                                                                                                              |  |

| 250 nH  | 0402                                                                                    | Gain Tilt (with R7 & R14). Coilcraft 0402AF-251XJLU                                                                                                                                         |  |

| 22 nH   | 0402                                                                                    | Input Match Stage2 Amp                                                                                                                                                                      |  |

| 22 nH   | 0402                                                                                    | Output Match Stage1 Amp                                                                                                                                                                     |  |

| 27 nH   | 0402                                                                                    | Input Match Stage1 Amp                                                                                                                                                                      |  |

| 33 nH   | 0402                                                                                    | Output Match Stage2 Amp                                                                                                                                                                     |  |

| 0 Ω     | 0402                                                                                    | Input Match                                                                                                                                                                                 |  |

| 30 Ω    | 0402                                                                                    | Increase value can reduce stage 2 current                                                                                                                                                   |  |

| 3 kΩ    | 0402                                                                                    | Voltage divider to set V <sub>DD</sub> _CMOS <sup>13</sup>                                                                                                                                  |  |

| 5 kΩ    | 0402                                                                                    | Voltage divider to set V <sub>DD</sub> _CMOS <sup>13</sup>                                                                                                                                  |  |

| 249 Ω   | 0402                                                                                    | Gain Tilt (with L2, L11)                                                                                                                                                                    |  |

| 22 Ω    | 0402                                                                                    | Gain Tilt (with C3, C19)                                                                                                                                                                    |  |

| 10 kΩ   | 0402                                                                                    | Increase value can reduce stage 1 current.                                                                                                                                                  |  |

| 50 Ω    | 0402                                                                                    | Drop V <sub>CC</sub> 1 to 5 V. Pdiss 1/20 W. 0 $\Omega$ for 5 V V <sub>CC</sub>                                                                                                             |  |

| 150 Ω   | 0402 or<br>0603                                                                         | Additional feedback resistors for Stage1 & Stage2 May be used to adjust gain or implement temperate compensation if replaced with thermistors.                                              |  |

| 1:2     |                                                                                         | MABA-011050                                                                                                                                                                                 |  |

|         | 1 μF 1 pF 47 μH 250 nH 22 nH 22 nH 27 nH 33 nH 0 Ω 30 Ω 3 kΩ 5 kΩ 249 Ω 22 Ω 10 kΩ 50 Ω | 150 pF 0402  1 μF 0805  1 pF 0402  47 μΗ 0806  250 nH 0402  22 nH 0402  22 nH 0402  27 nH 0402  33 nH 0402  30 Ω 0402  3 kΩ 0402  5 kΩ 0402  249 Ω 0402  10 kΩ 0402  150 Ω 0402  150 Ω 0402 |  |

<sup>13.</sup> These components may be omitted if 5 V supply is available for  $V_{\mbox{\scriptsize DD\_}}\mbox{\footnotesize CMOS}.$

Rev. V2

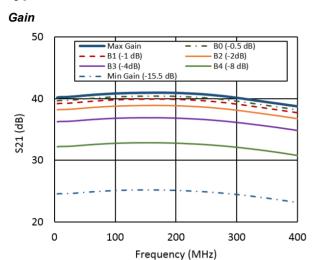

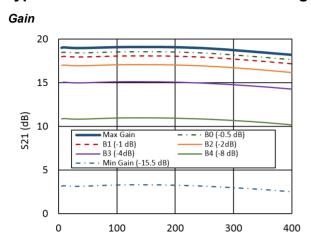

### **Typical Performance Curves:**

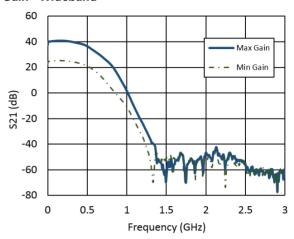

#### Gain - Wideband

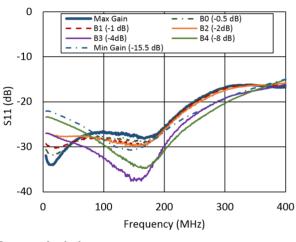

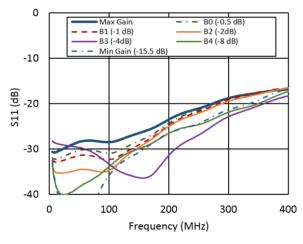

#### Input Return Loss

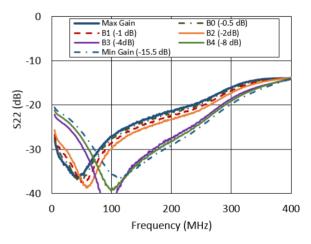

#### **Output Return Loss**

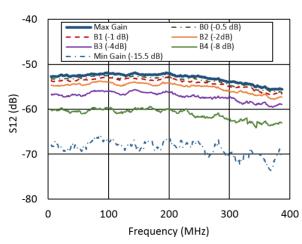

#### Reverse Isolation

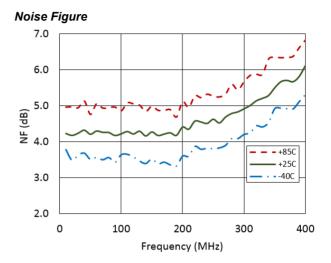

#### Noise Figure

Rev. V2

### **Typical Performance Curves:**

### Modulation Error Ratio (64 QAM, single channel)

### Modulation Error Ratio (64 QAM, 32 channel)

#### OIP3, OIP2

### Modulation Error Ratio (64 QAM, 16 channel)

Pout @ 30 dB Modulation Error Ratio

Rev. V2

### Lead-Free 7 mm 48-lead PQFN

<sup>†</sup> Reference Application Note S2083 for lead-free solder reflow recommendations. Meets JEDEC moisture sensitivity level 3 requirements. Plating is NiPdAuAg.

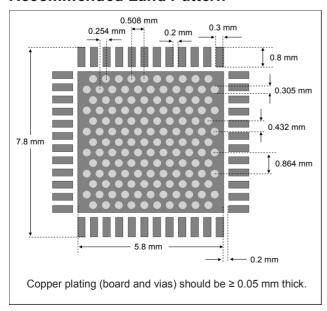

### Recommended Land Pattern

### **Handling Procedures**

Please observe the following precautions to avoid damage:

### **Static Sensitivity**

Gallium Arsenide Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these HBM Class 1B devices.

Rev. V2

### **Applications Section**

### **First Stage Bypass Application**

If a lower gain VGA solution is desired the MAAM-011168 may be implemented with the first stage bypassed. Typical Performance and Application Details for implementing the First Stage Bypass Application are presented below.

### Typical Performance: $T_A$ = +25°C, $V_{CC}$ = 8 V, minimum attenuation state, $Z_0$ = 75 $\Omega$

| Parameter               | Test Conditions                                                                                                                                                        | Units | Typical              |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|

| Gain                    | Max. Gain State @ 100 MHz, -29 dBm P <sub>IN</sub>                                                                                                                     | dB    | 19                   |

| Gain Slope              | Positive tilt from 5 - 250 MHz                                                                                                                                         | dB    | 0                    |

| Input Return Loss       | _                                                                                                                                                                      | dB    | 22                   |

| Output Return Loss      | _                                                                                                                                                                      | dB    | 22                   |

| Noise Figure            | _                                                                                                                                                                      | dB    | 4.3                  |

| Attenuation Range       | 100 MHz, Relative to maximum gain, -29 dBm P <sub>IN</sub>                                                                                                             |       | 15.5                 |

| 64 QAM MER <sup>7</sup> | 39 Channels (5 - 250 MHz), 51 dBmV/Ch.<br>Single Channel (8 - 200 MHz), 71 dBmV/Ch.<br>Single Channel (250 MHz), 70 dBmV/Ch.<br>16 Channels (5 - 250 MHz), 56 dBmV/Ch. |       | 36<br>35<br>35<br>34 |

| P1dB                    | _                                                                                                                                                                      |       | 27                   |

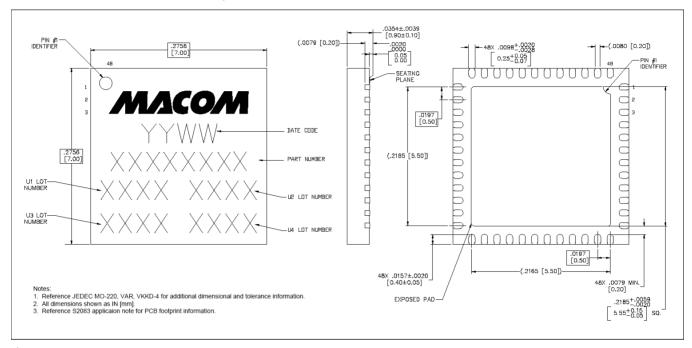

| OIP2                    | 2-tone,12 dBm/tone, 1 MHz tone spacing, 200 MHz                                                                                                                        |       | 76                   |

| OIP3                    | 2-tone,12 dBm/tone, 1 MHz tone spacing, 200 MHz                                                                                                                        |       | 46                   |

| Icc                     | EN1 = EN2 = 5 V                                                                                                                                                        | mA    | 225                  |

Rev. V2

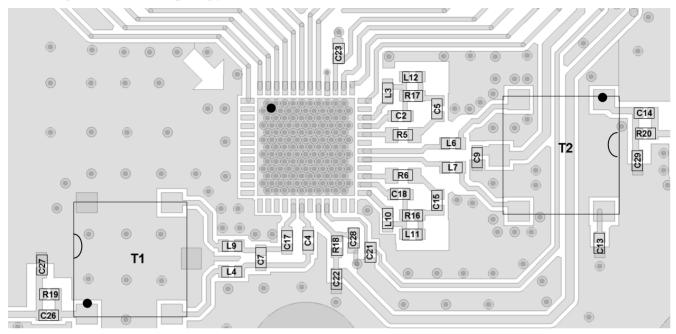

### **PCB Layout: First Stage Bypass**

### **Application Schematic: First Stage Bypass**

# Differential CATV Variable Gain Amplifier 5 - 300 MHz

Rev. V2

### Parts List: First Stage Bypass

| Part                        | Value  | Case Style   | Function/Notes                                                                                                                                    |

|-----------------------------|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| C9, C13, C21, C22, C23, C28 | 0.1 μF | 0402         | RF Bypass                                                                                                                                         |

| C2, C4, C5, C15, C17, C18   | 0.1 μF | 0402         | DC Block                                                                                                                                          |

| C14                         | 470 pF | 0402         | Gain Flatness                                                                                                                                     |

| C25                         | 1 µF   | 0805         | Low Frequency Bypass                                                                                                                              |

| C27, C29                    | 1pF    | 0402         | Input, Output Matching                                                                                                                            |

| C26                         | 270 pF | 0402         | Gain Flatness                                                                                                                                     |

| C7                          | DNI    | -            | Matching if needed                                                                                                                                |

| L3, L10                     | 18 nH  | 0402         | Input Match Stage2 Amp                                                                                                                            |

| L4, L9                      | 22 nH  | 0402         | Input Match DSA                                                                                                                                   |

| L6, L7                      | 24 nH  | 0402         | Output Match Stage2 Amp                                                                                                                           |

| L11, L12                    | 120 nH | 0402         | Gain Flatness                                                                                                                                     |

| R18                         | 30 Ω   | 0402         | Increase value can reduce stage 2 current                                                                                                         |

| R19, R20                    | 6.8 Ω  | 0402         | Gain Flatness                                                                                                                                     |

| R2                          | 3 kΩ   | 0402         | Voltage divider to set V <sub>DD</sub> _CMOS <sup>13</sup>                                                                                        |

| R4                          | 5 kΩ   | 0402         | Voltage divider to set V <sub>DD</sub> _CMOS <sup>13</sup>                                                                                        |

| R16, R17                    | 100 Ω  | 0402         | Gain Flatness                                                                                                                                     |

| R5, R6                      | 150 Ω  | 0402 or 0603 | Additional feedback resistors for Stage1 & Stage2. May be used to adjust gain or implement temperature compensation if replaced with thermistors. |

| T1, T2                      | 1:2    |              | MABA-011050                                                                                                                                       |

Rev. V2

### Typical Performance Curves: First Stage Bypass Application

Frequency (MHz)

#### Input Return Loss

### **Output Return Loss**

### OIP3, OIP2

#### MER vs Pout - 16 Channels

Rev. V2

# Functionality Modes of Operation: Serial, Direct Parallel, and Latched Parallel

#### **Mode Truth Table**

| P/S | LE            | Mode             |

|-----|---------------|------------------|

| 1   | X             | Serial           |

| 0   | Constant High | Direct Parallel  |

| 0   | Pulsed        | Latched Parallel |

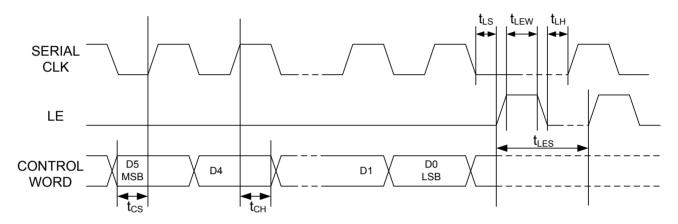

### Serial Mode

The serial control interface (SERIN, CLK, LE, SEROUT) is compatible with the SPI protocol. SPI mode is activated when P/S is kept high. The 6-bit serial word must be loaded with MSB first. After shifting in the 6 bit word, bringing LE high will set the attenuator to the desired state. While LE is high the CLK is masked to protect the data while implementing the change. SEROUT is the SERIN delayed by 6 clock cycles.

When P/S is low, the serial control interface is disabled and the serial input register is loaded asynchronously with parallel digital inputs.

### Direct Parallel Mode

The parallel mode is enabled when P/S is set to low. In the direct parallel mode, the attenuator is controlled by the parallel control inputs directly. The LE must be at logic high to control the attenuator in this mode.

#### Latched Parallel Mode

In the latched parallel mode, the parallel control inputs will be buffered by registers, and loaded to the outputs when LE is high. The outputs shall not change states when LE is low.

### Power-up States

The power-up (PUP) states will work in both serial and parallel modes, and initiate the attenuator according to the PUP truth table. During power up, the digital inputs shall be held constant for at least 1  $\mu$ s after V<sub>CC</sub> reaches 90% of final value. For serial mode, the PUP states will only work when LE is held low. The PUP state shall be locked out after the first LE pulse. Proper operation of power up states requires fast rise time (<200 ns) for V<sub>DD</sub>-CMOS.

Rev. V2

# Functionality Modes of Operation: Serial, Direct Parallel, and Latched Parallel

### **PUP Truth Table**

|    | Inputs |      |        | Onlin Bulation to Many Onlin | Nata          |

|----|--------|------|--------|------------------------------|---------------|

| PS | LE     | PUP2 | PUP1   | Gain Relative to Max. Gain   | Notes         |

| 0  | 0      | 0    | 0      | -15.5 dB                     |               |

| 0  | 0      | 0    | 1      | -8 dB                        |               |

| 0  | 0      | 1    | 0 0 dB |                              | Parallel Mode |

| 0  | 0      | 1    | 1      | 0 dB                         |               |

| 0  | 1      | Х    | Х      | 0 to -15.5 dB (Set B0 - B4)  |               |

| 1  | 0      | Х    | Х      | 0 to -15.5 dB (Set B0 - B4)  | Carial Mada   |

| 1  | 1      | Х    | Х      | No Definition                | Serial Mode   |

### **Serial Interface Timing Characteristics**

| Symbol           | Parameter                           | Т     | Units |       |       |

|------------------|-------------------------------------|-------|-------|-------|-------|

| Symbol           | Farameter                           | -40°C | +25°C | +85°C | Units |

| t <sub>sck</sub> | Min. Serial Clock Period            | 100   | 100   | 100   | ns    |

| t <sub>CS</sub>  | Min. Control Set-up Time            | 20    | 20    | 20    | ns    |

| t <sub>CH</sub>  | Min. Control Hold Time              | 20    | 20    | 20    | ns    |

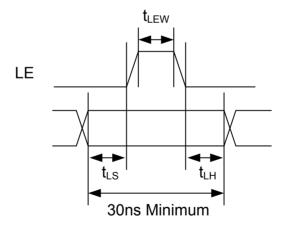

| t <sub>LS</sub>  | Min. LE Set-up Time                 | 10    | 10    | 10    | ns    |

| t <sub>LEW</sub> | Min. LE Pulse Width                 | 10    | 10    | 10    | ns    |

| t <sub>LH</sub>  | Min. Serial Clock Hold Time from LE | 10    | 10    | 10    | ns    |

| t <sub>LES</sub> | Min. LE Pulse Spacing               | 630   | 630   | 630   | ns    |

Rev. V2

# Functionality Modes of Operation: Serial, Direct Parallel, and Latched Parallel

### **Serial Input Interface Timing Diagram**

### **Parallel Control Word**

Differential CATV Variable Gain Amplifier 5 - 300 MHz

Rev. V2

### M/A-COM Technology Solutions Inc. All rights reserved.

Information in this document is provided in connection with M/A-COM Technology Solutions Inc ("MACOM") products. These materials are provided by MACOM as a service to its customers and may be used for informational purposes only. Except as provided in MACOM's Terms and Conditions of Sale for such products or in any separate agreement related to this document, MACOM assumes no liability whatsoever. MACOM assumes no responsibility for errors or omissions in these materials. MACOM may make changes to specifications and product descriptions at any time, without notice. MACOM makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppels or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MACOM FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MACOM SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.