MAAD-011048

Rev. V3

#### **Features**

- 5-Bit, 1 dB LSB, 31 dB range

- Insertion Loss:

2.0 dB @ 26.5 GHz

3.1 dB @ 50 GHz

- P0.1 dB: 26 dBm @ 40 GHz

- Integrated CMOS Compatible Driver

- Compatible with 1.8 V CMOS logic

- Parallel or Serial (P/S) Control

- Low DC Power Consumption

- Lead-Free 3 mm 20-Lead Package

- RoHS\* Compliant

### **Applications**

- ISM

- Multi Market

### **Description**

The MAAD-011048 is a wide band 5-bit, 1 dB step MMIC digital attenuator in a lead-free 3 mm, 20 lead surface mount laminate package. This device is ideally suited for use where high accuracy, very low power consumption, and low intermodulation products are required.

This attenuator is controlled with either a SPI compatible serial interface or a 5 bit parallel word. SEROUT is the SERIN delayed by 6 clock cycles which can be used in daisy-chain operation.

## Ordering Information<sup>1,2</sup>

| Part Number        | Package        |

|--------------------|----------------|

| MAAD-011048-TR0500 | 500 piece reel |

| MAAD-011048-SB1    | Sample Board   |

- 1. Reference Application Note M513 for reel size information.

- 2. All sample boards include 3 loose parts.

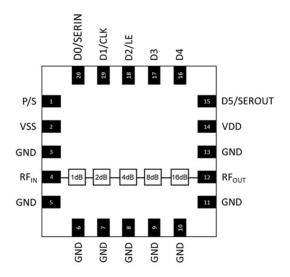

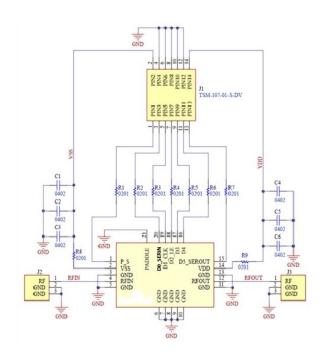

### **Functional Schematic**

## Pin Configuration<sup>3</sup>

| Pin #         | Function                   |  |

|---------------|----------------------------|--|

| 1             | Parallel/Serial Selection  |  |

| 2             | Negative Supply            |  |

| 3, 5 - 11, 13 | Ground                     |  |

| 4             | RF Input                   |  |

| 12            | RF Output                  |  |

| 14            | Positive Supply            |  |

| 15            | 16 dB bit or Serial Output |  |

| 16            | 8 dB Bit Control           |  |

| 17            | 4 dB Bit Control           |  |

| 18            | 2 dB Bit or LE             |  |

| 19            | 1 dB Bit or Clock          |  |

| 20            | Serial Input               |  |

| 214           | Ground Pad                 |  |

|               |                            |  |

- MACOM recommends connecting unused package pins to ground.

- The exposed pad centered on the package bottom must be connected to RF, DC and thermal ground.

<sup>\*</sup> Restrictions on Hazardous Substances, compliant to current RoHS EU directive.

MAAD-011048

Rev. V3

## **Pin Description**

| Pin#          | Name              | Description                                                                                              |

|---------------|-------------------|----------------------------------------------------------------------------------------------------------|

| 1             | P/S               | Selection of serial or parallel control mode                                                             |

| 2             | VSS               | Negative supply Input                                                                                    |

| 3,<br>5~11,13 | GND               | Ground. The GND pins must be connected to the RF and DC ground of the PCB                                |

| 4             | RF <sub>IN</sub>  | Attenuator Input. The RF <sub>IN</sub> pin is DC-coupled to 0 V and AC matched to 50 Ω. No DC blocking   |

| 12            | RF <sub>OUT</sub> | Attenuator Output. The RF <sub>OUT</sub> pin is DC-coupled to 0 V and AC matched to 50 Ω. No DC blocking |

| 14            | VDD               | Positive supply Input                                                                                    |

| 15            | D5/<br>SEROUT     | Parallel control input for 16 dB attenuation bit or serial input control delayed by 6 clock cycles       |

| 16            | D4                | Parallel control input for 8 dB attenuation bit                                                          |

| 17            | D3                | Parallel control input for 4 dB attenuation bit                                                          |

| 18            | D2/LE             | Parallel control input for 2 dB attenuation bit or latch enable input of serial control mode             |

| 19            | D1/CLK            | Parallel control input for 1 dB attenuation bit or clock input of serial control mode                    |

| 20            | SERIN             | Control word input of serial control mode                                                                |

| 21            | Pad               | Exposed Pad. The exposed pad must be connected to the RF and DC ground of the PCB                        |

MAAD-011048

Rev. V3

## **AC Electrical Specifications:**

$T_A = 25^{\circ}C$ , VDD = +3.3 V, VSS= -3.3 V<sup>5</sup>,  $P_{IN} = 0$  dBm,  $Z_0 = 50 \Omega$

| Parameter                             | Test Conditions                                                                           | Units                | Min.        | Тур.                                                             | Max.                       |

|---------------------------------------|-------------------------------------------------------------------------------------------|----------------------|-------------|------------------------------------------------------------------|----------------------------|

| Reference Insertion Loss              | DC - 18.0 GHz<br>18.0 - 26.5 GHz<br>26.5 - 40.0 GHz<br>40.0 - 50.0 GHz<br>50.0 - 55.0 GHz | dB                   | _           | 1.5<br>2.0<br>2.4<br>3.1<br>3.1                                  | 2.6<br>3.2<br>3.8<br>4.7   |

| RMS Attenuation Error                 | DC - 18.0 GHz<br>18.0 - 26.5 GHz<br>26.5 - 40.0 GHz<br>40.0 - 55.0 GHz                    | dB                   | _           | 0.4<br>0.7<br>0.9<br>0.7                                         | _                          |

| Attenuation Accuracy                  | DC - 18.0 GHz<br>18.0 - 26.5 GHz<br>26.5 - 40.0 GHz<br>40.0 - 55.0 GHz                    | ± (0.3 +<br>± (0.3 + | 3% of atten | uation settin<br>uation settin<br>uation settin<br>uation settin | ıg) dB typ.<br>ıg) dB typ. |

| Input Return Loss                     | All states                                                                                | dB                   | _           | -15                                                              | _                          |

| Output Return Loss                    | All states                                                                                | dB                   | _           | -12                                                              | _                          |

| Input P0.1dB                          | 10 GHz @ Reference State                                                                  | dBm                  | _           | 27                                                               | _                          |

| IIP₃ @ 10 GHz                         | 2-Tone, +7 dBm/tone,<br>1 MHz Spacing (Reference State)                                   | dBm                  | _           | 50                                                               | _                          |

| T <sub>RISE</sub> , T <sub>FALL</sub> | 10% to 90% RF, 90% to 10% RF                                                              | ns                   | _           | 15                                                               | _                          |

| T <sub>ON</sub> , T <sub>OFF</sub>    | 50% triggered control to 90%, 10% of RF                                                   | ns                   | _           | 125                                                              | _                          |

| Overshoot                             | All state changes                                                                         | dB                   |             | 2.8                                                              |                            |

| Undershoot                            | All state changes                                                                         | dB                   | _           | -10                                                              | _                          |

<sup>5.</sup> Apply VDD and VSS before RF signal. No sequence requirement for VDD & VSS.

## DC Electrical Specifications: $T_A = 25$ °C, VDD = +3.3 V, VSS = -3.3 V

| Parameter                          | Test Conditions         | Units | Min. | Тур. | Max. |

|------------------------------------|-------------------------|-------|------|------|------|

| I <sub>DD</sub> Quiescent Current  | _                       | mA    | _    | 0.3  |      |

| I <sub>ss</sub> Quiescent Current  | _                       | mA    | _    | 0.6  | _    |

| Logic Input High V <sub>IH</sub>   | _                       | V     | 1.17 | _    | 2    |

| Logic Input Low V <sub>IL</sub>    | _                       | V     | 0    | _    | 0.8  |

| Logic Input Current                | V <sub>IH</sub> = 1.8 V | μA    | _    | _    | 10   |

| SEROUT Output High V <sub>OH</sub> | 18 KΩ load              | V     | _    | 1.8  | _    |

| SEROUT Output Low V <sub>OL</sub>  | 18 KΩ load              | V     | _    | 0    | _    |

Rev. V3

### **Recommended Operating Conditions**

| Parameter                                                                 | Symbol         | Unit | Min.  | Тур. | Max.  |

|---------------------------------------------------------------------------|----------------|------|-------|------|-------|

| Input Power, 100 MHz to 40 GHz (RF $_{\rm IN}$ and RF $_{\rm OUT}$ ) $^6$ | -              | dBm  | _     |      | 26    |

| Positive Supply Voltage                                                   | VDD            | V    | +3.15 | +3.3 | +3.45 |

| Negative Supply Voltage                                                   | VSS            | V    | -3.45 | -3.3 | -3.15 |

| Operating Temperature <sup>7</sup>                                        | T <sub>c</sub> | °C   | -40   | 25   | 105   |

## Absolute Maximum Ratings<sup>8,9</sup>

| Parameter                          | Symbol         | Unit | Min. | Max. |

|------------------------------------|----------------|------|------|------|

| Input Power                        | -              | dBm  | _    | 27   |

| Positive Supply Voltage            | VDD            | V    | -0.3 | 3.6  |

| Negative Supply Voltage            | VSS            | V    | -3.6 | +0.3 |

| Logic Input Voltage                | Vı             | V    | -0.2 | +2   |

| Operating Temperature <sup>7</sup> | T <sub>c</sub> | °C   | -40  | 105  |

| Storage Temperature                | -              | °C   | -65  | 150  |

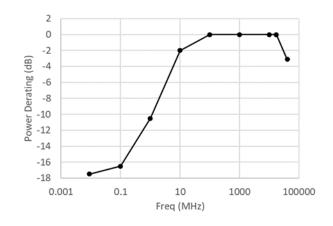

<sup>6.</sup> T<sub>PADDLE</sub> = +105°C. See power derating curve for details.

7. Temperature of the exposed pad.

## **Power Derating Curve**

### **Handling Procedures**

Please observe the following precautions to avoid damage:

### Static Sensitivity

These electronic devices are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these devices.

| Parameter                     | Rating   | Standard             |

|-------------------------------|----------|----------------------|

| Human Body<br>Model (HBM)     | Class 1B | ESDA/JEDEC<br>JS-001 |

| Charged Device<br>Model (CDM) | Class C3 | ESDA/JEDEC<br>JS-002 |

<sup>8.</sup> Exceeding any one or combination of these limits may cause permanent damage to this device.

<sup>9.</sup> MACOM does not recommend sustained operation near these survivability limits.

Rev. V3

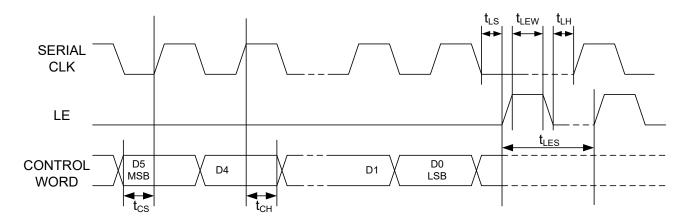

### Modes of Operation: Serial and Direct Parallel

### **Serial Mode**

The serial control interface (SERIN, CLK, LE, SEROUT) is compatible with the SPI protocol. SPI mode is activated when P/S is kept high. The 6-bit serial word must be loaded with the MSB first. After shifting in the 6 bit word, a rising edge on LE will set the attenuator to the desired state. While LE is high the CLK is masked to protect the data while implementing the change. SEROUT is SERIN delayed by 6 clock cycles.

When P/S is low, the serial control interface is disabled. When P/S is set high, pins 18, 19, & 20 have the LE, CLK, and SER IN functions, respectively.

In serial mode operation, the outputs will stay constant while LE is kept low.

#### **Direct Parallel Mode**

The parallel mode is enabled when P/S is set low. In the direct parallel mode, the phase shifter is controlled by the parallel control inputs directly. When P/S is set low, pins 18 & 19 have the D2 & D1 functions.

### **Mode Truth Table**

| P/S | LE  | Mode            |

|-----|-----|-----------------|

| 1   | X   | Serial          |

| 0   | N/A | Direct Parallel |

### Truth Table 10

| D5 | D4 | D3 | D2 | D1 | D0 | Attenuation (dB) |

|----|----|----|----|----|----|------------------|

| 0  | 0  | 0  | 0  | 0  | Х  | Reference IL     |

| 0  | 0  | 0  | 0  | 1  | Х  | 1                |

| 0  | 0  | 0  | 1  | 0  | Х  | 2                |

| 0  | 0  | 1  | 0  | 0  | Х  | 4                |

| 0  | 1  | 0  | 0  | 0  | Х  | 8                |

| 1  | 0  | 0  | 0  | 0  | Х  | 16               |

| 1  | 1  | 1  | 1  | 1  | Х  | 31               |

10."0" =  $V_{IL}$ , "1" =  $V_{IH}$ .

## Functionality Modes of Operation: Serial and Direct Parallel

### **Serial Input Interface Timing Diagram**

MAAD-011048

Rev. V3

## **Serial Interface Timing Characteristics**

| 0                | Complete Bourses                    |       | Typical Performance |       |       |  |

|------------------|-------------------------------------|-------|---------------------|-------|-------|--|

| Symbol           | Parameter                           | -40°C | +25°C               | +85°C | Units |  |

| t <sub>sck</sub> | Min. Serial Clock Period            | 100   | 100                 | 100   | ns    |  |

| t <sub>CS</sub>  | Min. Control Set-up Time            | 20    | 20                  | 20    | ns    |  |

| t <sub>CH</sub>  | Min. Control Hold Time              | 20    | 20                  | 20    | ns    |  |

| t <sub>LS</sub>  | Min. LE Set-up Time                 | 10    | 10                  | 10    | ns    |  |

| t <sub>LEW</sub> | Min. LE Pulse Width                 | 10    | 10                  | 10    | ns    |  |

| t <sub>LH</sub>  | Min. Serial Clock Hold Time from LE | 10    | 10                  | 10    | ns    |  |

| t <sub>LES</sub> | Min. LE Pulse Spacing               | 630   | 630                 | 630   | ns    |  |

Rev. V3

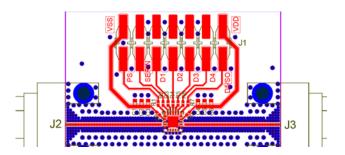

## **PCB Layout**

## Parts List

| Part    | Value                      | Case Style                  |

|---------|----------------------------|-----------------------------|

| AT1     | MAAD-011048                | 3 mm, 20 Lead               |

| C1, C6  | Capacitor,<br>1 µF, 50 V   | 0402                        |

| C2, C5  | Capacitor,<br>10 nF, 50 V  | 0402                        |

| C3, C4  | Capacitor,<br>100 pF, 50 V | 0402                        |

| R1 - R9 | Resistor, 0 Ω              | 0201                        |

| J2 - J3 | Southwest<br>1492-03A-5    | End Launch<br>2.4 mm Female |

| J1      | DC Connector               | TSM-107-01-S-DV             |

## **Application Schematic**

Rev. V3

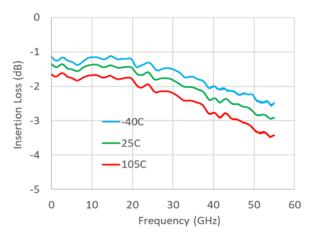

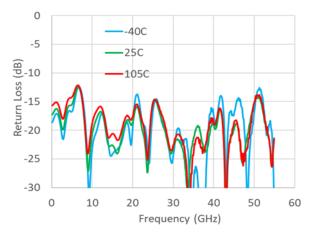

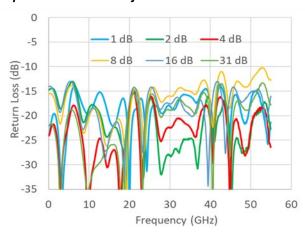

## **Typical Performance Curves**

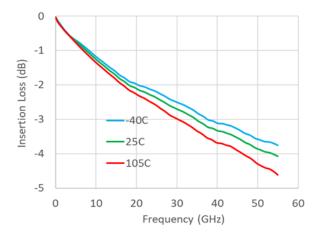

### Insertion Loss

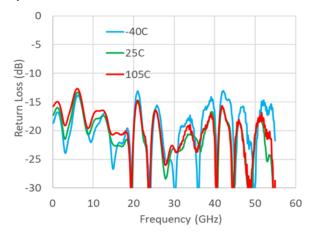

#### Output Return Loss - Reference State

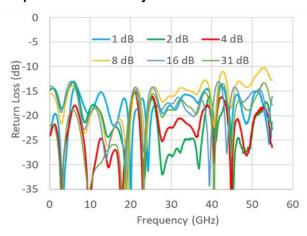

### Input Return Loss - Major Bits

### Input Return Loss - Reference State

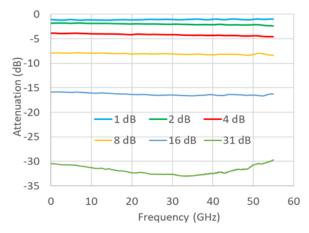

### Attenuation - Major Bits

### Output Return Loss - Major Bits

Rev. V3

### **Typical Performance Curves**

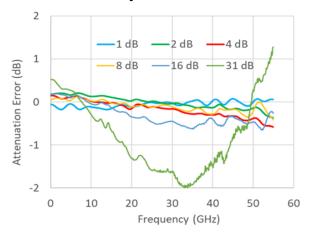

### Attenuation Error - Major Bits

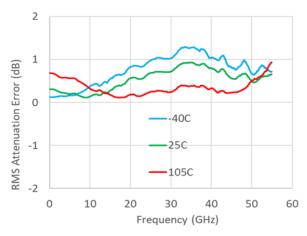

#### RMS Attenuation Error

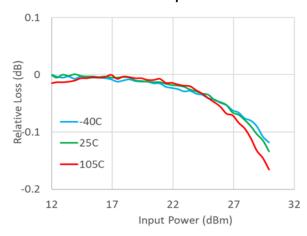

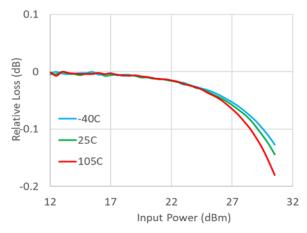

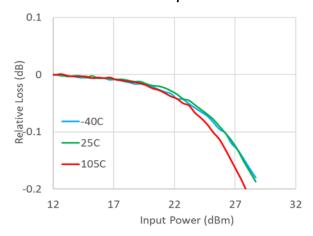

Ref. State Insertion Loss Compression - 10 GHz

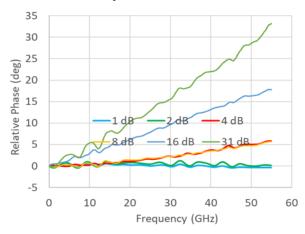

### Relative Phase - Major Bits

Ref. State Insertion Loss Compression - 100 MHz

Ref. State Insertion Loss Compression - 40 GHz

Rev. V3

## **Typical Performance Curves**

### **Evaluation Board Thru Line Insertion Loss**

Rev. V3

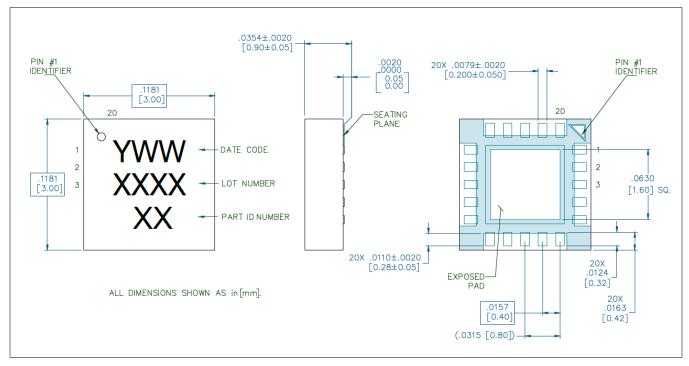

## Lead-Free 3 mm, 20-Lead Laminate Package<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> Reference Application Note S2083 for lead-free solder reflow recommendations. Meets JEDEC moisture sensitivity level 3 requirements in accordance to JEDEC J-STD-020D. Plating is 100% NiPdAg over copper.

MAAD-011048

Rev. V3

### MACOM Technology Solutions Inc. ("MACOM"). All rights reserved.

These materials are provided in connection with MACOM's products as a service to its customers and may be used for informational purposes only. Except as provided in its Terms and Conditions of Sale or any separate agreement, MACOM assumes no liability or responsibility whatsoever, including for (i) errors or omissions in these materials; (ii) failure to update these materials; or (iii) conflicts or incompatibilities arising from future changes to specifications and product descriptions, which MACOM may make at any time, without notice. These materials grant no license, express or implied, to any intellectual property rights.

THESE MATERIALS ARE PROVIDED "AS IS" WITH NO WARRANTY OR LIABILITY, EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHT, ACCURACY OR COMPLETENESS, OR SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES WHICH MAY RESULT FROM USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.