### M08046

# SD, HD, and 3G Cable Equalizer

The M08046 is a high-speed, low-power, adaptive co-axial cable equalizer designed to increase the maximum low-jitter transmission distance of serial digital interface (SDI) video signals across commonly used bandwidth-limiting 75  $\Omega$  coaxial cable. This device automatically optimizes its transfer function based on the bit rate and cable length to minimize the inter-symbol interference (ISI) jitter caused by the cable and to remove the DC offset components introduced with the pathological test pattern and AC coupling in systems.

The M08046 is designed to support SD, HD, and 3G data rates from 143 Mbps to 2970 Mbps.

The low-noise, high-gain equalizer allows for low jitter 3G-SDI transmissions up to 100 m (Belden 1694A) and HD transmissions up to a length of 200 m (Belden 1694A) and 120 m (Belden 8281). For SD data rates, cable lengths up to 400 m (Belden 1694A) and 300 m (Belden 8281) are supported.

### **Applications**

- · Digital Video Recorders (DVR)

- · Video Mixers and Switchers

- · Surveillance / CCTV Cameras

- · Industrial and Professional Cameras

- · Digital Image Capture Devices

- · Digital Video Displays

- · Distribution Amplifiers

- · Repeaters

#### **Features**

- · Dual CML outputs, with selectable high amplitude

- · Enable for second CML output

- 2.5 V or 3.3 V Supply

- Low Power (175 mW @ 2.5 V, 230 mW @ 3.3 V)

- · Adaptive cable equalization

- · 3G. HD. and SD operation

- Typical equalized length of Belden 1694A cable: 100 m at 2.97 Gbps, 200 m at 1.485 Gbps, and 400 m at 270 Mbps

- · Programmable mute level

- · Manual bypass mode

- Small form factor (5x5 mm, 32-pin QFN package)

- · Pb-free and RoHS compliant

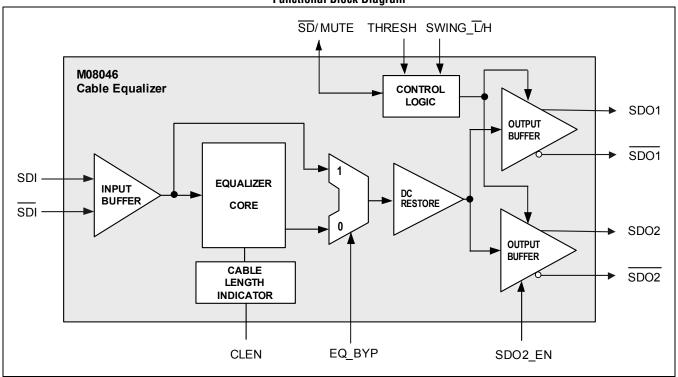

#### **Functional Block Diagram**

# **Ordering Information**

| Part Number                                                                                                                                   | Package                     | Operating Data Rate | Operating Temperature |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------|-----------------------|--|--|--|--|

| M08046G-11*                                                                                                                                   | 32-pin QFN (RoHS compliant) | 143-2970 Mbps       | −10 °C to 85 °C       |  |  |  |  |

| * The letter 'G' designator after the part number indicates an RoHS-compliant package. Refer to www.mindspeed.com for additional information. |                             |                     |                       |  |  |  |  |

# **Revision History**

| Revision | Level   | Date     | Description      |

|----------|---------|----------|------------------|

| Α        | Release | May 2011 | Initial Release. |

### M08046 Marking Diagram

# **Table of Contents**

| Order | ing   | Informa   | ation                                               | 2  |

|-------|-------|-----------|-----------------------------------------------------|----|

| Revis | ion l | History.  |                                                     | 2  |

| Table | of C  | ontents   | S                                                   | 3  |

|       |       |           |                                                     |    |

|       | Ŭ     |           |                                                     |    |

|       |       |           | haracteristics                                      |    |

|       |       |           | gram, Pin Descriptions, and Package Outline Drawing |    |

|       |       | _         |                                                     |    |

|       | 2.1   |           | scriptions                                          |    |

|       | 2.2   |           | ge Drawingactureability                             |    |

|       | 2.3   | 2.3.1     | Electrostatic Discharge.                            |    |

|       |       | 2.3.1     | Peak Reflow Temperature                             |    |

|       |       | 2.3.3     | Moisture Sensitivity Level (MSL)                    |    |

| 3.0   | Fun   | ctional I | Description                                         | 16 |

|       | 3.1   | Pin Des   | scriptions                                          | 16 |

|       |       | 3.1.1     | General Nomenclature                                | 16 |

|       |       | 3.1.2     | High-Speed Input                                    | 16 |

|       |       | 3.1.3     | High-Speed Outputs                                  |    |

|       |       | 3.1.4     | Adaptive Equalization Selection                     |    |

|       |       | 3.1.5     | Cable Length Indicator                              |    |

|       |       | 3.1.6     | Output Mute and Signal Detect.                      |    |

|       |       | 3.1.7     | Equalizer Detailed Description                      |    |

| Appei | ndıx  |           |                                                     | 19 |

|       | A.1   | Glossar   | ry of Terms/Acronyms                                |    |

|       | A.2   | Referer   | nce Documents                                       |    |

|       |       | Δ21       | External                                            | 20 |

# **List of Figures**

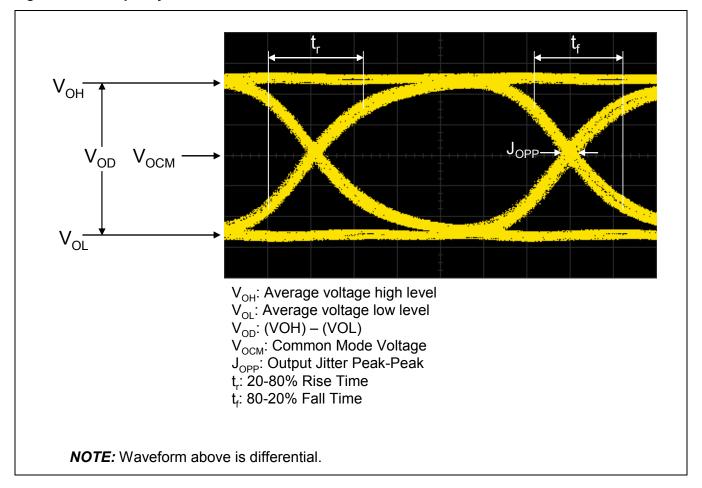

| Figure 1-1. | Output Symbols Definition                               | 9  |

|-------------|---------------------------------------------------------|----|

| Figure 2-1. | M08046 Pin Assignments                                  | 11 |

| Figure 2-2. | M08046 Packaging Details—Amkor                          | 14 |

| Figure 3-1. | Single-ended Typical Input Matching/Termination Network | 16 |

| Figure 3-2. | Test Setup Diagram for Cable Equalizer Evaluation       | 18 |

# **List of Tables**

| Table 1-1. | Absolute Maximum Ratings                                  | 6  |

|------------|-----------------------------------------------------------|----|

| Table 1-2. | Recommended Operating Conditions                          |    |

| Table 1-3. | Power DC Electrical Specifications                        | 6  |

| Table 1-4. | CMOS Input Electrical Specifications (Logic Signals Only) | 7  |

| Table 1-5. | High Speed Input Electrical Specifications                | 7  |

| Table 1-6. | High Speed Output Electrical Specifications               | 8  |

| Table 1-7. | Cable Equalizer Distance Specifications                   | 10 |

| Table 1-8. | xSD/MUTE Output Specifications                            | 10 |

| Table 2-1. | Power Pins                                                | 12 |

| Table 2-2. | High-speed Signal Pins                                    | 12 |

| Table 2-3. | Control/Interface Pins                                    | 13 |

# 1.0 Electrical Characteristics

Table 1-1. Absolute Maximum Ratings

| Symbol                | Parameter                                       | Minimum                | Maximum                | Units |

|-----------------------|-------------------------------------------------|------------------------|------------------------|-------|

| AV <sub>DD</sub>      | Positive Supply                                 | AV <sub>SS</sub> - 0.5 | AV <sub>SS</sub> + 3.6 | V     |

| V <sub>MAX, 10</sub>  | Maximum/minimum voltage on any input/output pin | AV <sub>SS</sub> - 0.5 | AV <sub>DD</sub> + 0.5 | V     |

| T <sub>STORE</sub>    | Storage Temperature                             | -65                    | +150                   | °C    |

| V <sub>ESD, HBM</sub> | Human Body Model (low-speed)                    | 2000                   | _                      | V     |

| V <sub>ESD, HBM</sub> | Human Body Model (high-speed)                   | 2000                   | _                      | V     |

| V <sub>ESD, CDM</sub> | Charge Device Model                             | 500                    | _                      | V     |

### Table 1-2. Recommended Operating Conditions

| Symbol           | Parameter                              | Notes | Minimum | Typical | Maximum | Units |

|------------------|----------------------------------------|-------|---------|---------|---------|-------|

| AV <sub>DD</sub> | Supply Voltage                         | _     | 2.37    | 2.5/3.3 | 3.47    | V     |

| T <sub>AMB</sub> | Ambient Temperature                    | _     | -10     | _       | +85     | °C    |

| $\theta_{JA}$    | Junction to Ambient Thermal Resistance | 1, 2  | _       | 40      | _       | °C/W  |

### NOTES:

### Table 1-3. Power DC Electrical Specifications

| Symbol             | Parameter                        | Notes   | Typical | Maximum | Units |

|--------------------|----------------------------------|---------|---------|---------|-------|

| I <sub>DD</sub>    | Supply Current                   | 1       | 70      | 90      | mA    |

| P <sub>TOTAL</sub> | Total Power Dissipation (@2.5 V) | 1, 2, 3 | 175     | 236     | mW    |

| P <sub>TOTAL</sub> | Total Power Dissipation (@3.3 V) | 1, 2, 3 | 230     | 312     | mW    |

#### NOTES:

- 1. Specified at recommended operating conditions See Table 1-2.

- 2. Includes on-chip power dissipation as well as off-chip power dissipated by termination resistors.

- 3. Typical calculated at nominal supply voltage, maximum calculated at nominal supply voltage + 5%.

<sup>.</sup> Mounted on multi layer board ( $\geq 4$  layers).

<sup>2.</sup> Airflow = 0.0 m/s.

Table 1-4. CMOS Input Electrical Specifications (Logic Signals Only)

| Symbol          | Parameter                  | Notes | Minimum                 | Maximum                 | Units |

|-----------------|----------------------------|-------|-------------------------|-------------------------|-------|

| V <sub>IH</sub> | Input Logic High Voltage   | 1     | 0.75 x AV <sub>DD</sub> | AV <sub>DD</sub> + 0.3  | V     |

| V <sub>IL</sub> | Input Logic Low Voltage    | 1     | 0                       | 0.25 x AV <sub>DD</sub> | V     |

| I <sub>IH</sub> | Input Current (logic high) | 1     | -100                    | 100                     | μΑ    |

| I <sub>IL</sub> | Input Current (logic low)  | 1     | -100                    | 100                     | μΑ    |

### NOTE:

### Table 1-5. High Speed Input Electrical Specifications

| Symbol              | Parameter                                                                 | Notes   | Minimum | Typical | Maximum | Units     |

|---------------------|---------------------------------------------------------------------------|---------|---------|---------|---------|-----------|

| DR                  | Input Bit Rate                                                            | 1       | 143     | _       | 2970    | Mbps      |

| V <sub>IN</sub>     | Input Voltage Range with 0 m of cable,<br>AV <sub>DD</sub> = 2.5 or 3.3 V | 1, 5    | 700     | 800     | 1200    | $mV_{PP}$ |

| V <sub>CM, IN</sub> | Input Common-Mode Voltage (AV <sub>DD</sub> = 3.3 V)                      | 1, 4    | _       | 2.75    | _       | V         |

|                     | Input Common-Mode Voltage (AV <sub>DD</sub> = 2.5 V)                      | 1, 4    | _       | 1.95    | _       | V         |

| C <sub>IN</sub>     | Input capacitance                                                         | 1, 4    | _       | 0.5     | _       | pF        |

| R <sub>IN</sub>     | Input resistance                                                          | 1, 4    | _       | 1.6     | _       | kΩ        |

| S <sub>11</sub>     | Input Return Loss (5 MHz to 1.5 GHz)                                      | 1, 2, 3 | 20      | 30      | _       | dB        |

|                     | Input Return Loss (1.5 GHz to 3 GHz)                                      | 1, 2, 3 | _       | 13      | _       | dB        |

### NOTES:

- 1. Specified at recommended operation conditions See Table 1-2.

- 2. Using the recommended input termination shown in Figure 3-1.

- 3. Measured single ended.

- 4. Guaranteed by design.

- 5. This is also the recommended cable launch level (far end).

<sup>1.</sup> Specified at recommended operating conditions — See Table 1-2. Spec is for a max load of 20 pF.

Table 1-6. High Speed Output Electrical Specifications

| Symbol                         | Parameter                                                  | Notes      | Minimum | Typical                  | Maximum | Units             |

|--------------------------------|------------------------------------------------------------|------------|---------|--------------------------|---------|-------------------|

| t <sub>R</sub> /t <sub>F</sub> | Rise/Fall Time (20%–80%)                                   | 1, 2, 7    | _       | 100                      | 120     | ps                |

| $t_R/t_F \Delta$               | Rise/Fall Time Mismatch                                    | 1, 2, 7    | _       | 0                        | 30      | ps                |

| DCD <sub>DATA</sub>            | Duty Cycle Distortion                                      | 1, 2, 5, 6 | _       | 0                        | 15      | ps                |

| V <sub>OD</sub>                | Differential Output Voltage<br>HiSwEn = 0 (750 mV)         | 1, 3       | 600     | 750                      | 950     | mV <sub>PPD</sub> |

| V <sub>OCM</sub>               | Common mode Voltage<br>HiSwEn = 0 (750 mV)                 | 1, 3, 4    | _       | AV <sub>DD</sub> - 0.205 | _       | V                 |

| V <sub>OD</sub>                | Differential Output Voltage<br>HiSwEn = 1 (1050 mV)        | 1, 3       | 850     | 1050                     | 1270    | mV <sub>PPD</sub> |

| V <sub>OCM</sub>               | Common mode Voltage<br>HiSwEn = 1 (1050 mV)                | 1, 3, 4    | _       | AV <sub>DD</sub> - 0.290 | _       | V                 |

| R <sub>OUT</sub>               | Internal Output Termination Resistance to AV <sub>DD</sub> | 1          | 40      | 50                       | 60      | Ω                 |

### NOTES:

- 1. Specified at recommended operation conditions See Table 1-2.

- 2. With 100  $\Omega$  differential termination.

- 3. With 50  $\Omega$  to  $\text{AV}_{\text{DD}}$  termination.

- 4. Outputs DC-coupled.

- 5. Duty Cycle Distortion is defined as the difference in the intrinsic jitter at the 50% voltage level and the intrinsic jitter at the rising/falling edge crossing point. If the rising/falling edge crossing point is at the 50% voltage level, then DCD<sub>DATA</sub> = 0.

- 6. Measured with a 1010 pattern.

- 7. Measured with a PRBS23 pattern.

Figure 1-1. Output Symbols Definition

Table 1-7. Cable Equalizer Distance Specifications

| Symbol          | Parameter    | Conditions   | Notes | Maximum | Units |

|-----------------|--------------|--------------|-------|---------|-------|

| L <sub>SD</sub> | Cable Length | Belden 1694A | 1, 4  | 400     | m     |

|                 | Cable Length | Belden 8281  | 1, 4  | 300     | m     |

| L <sub>HD</sub> | Cable Length | Belden 1694A | 2, 6  | 200     | m     |

|                 | Cable Length | Belden1694A  | 2, 5  | 140     | m     |

|                 | Cable Length | Belden 8281  | 2, 5  | 120     | m     |

| L <sub>3G</sub> | Cable Length | Belden 1694A | 3, 7  | 100     | m     |

#### **NOTES:**

Entire table specified at recommended operating conditions — See Table 1-2.

- 1. Data Rate = 270 Mbps.

- 2. Data Rate = 1485 Mbps.

- 3. Data Rate = 2970 Mbps.

- 4. Error Free with timing Jitter typically = 0.2 UI, pathological pattern.

- 5. Error Free with alignment Jitter typically = 0.25 UI, pathological pattern.

- 6. Error Free with alignment jitter typically = 0.3 UI, pathological pattern.

- 7. Error Free with alignment Jitter typically = 0.35 UI, pathological pattern.

### Table 1-8. xSD/MUTE Output Specifications

| Symbol               | Parameter                                     | Notes | Typical                 | Units |

|----------------------|-----------------------------------------------|-------|-------------------------|-------|

| V <sub>LOS, OH</sub> | Output voltage when input signal detected     | 1     | 0.16 x AV <sub>DD</sub> | V     |

| V <sub>LOS, OL</sub> | Output voltage when input signal not detected | 1     | 0.95 x AV <sub>DD</sub> | V     |

| IOTE:                |                                               |       |                         |       |

#### NOTE:

1. Specified at recommended operating condition — See Table 1-2.

# 2.0 Pinout Diagram, Pin Descriptions, and Package Outline Drawing

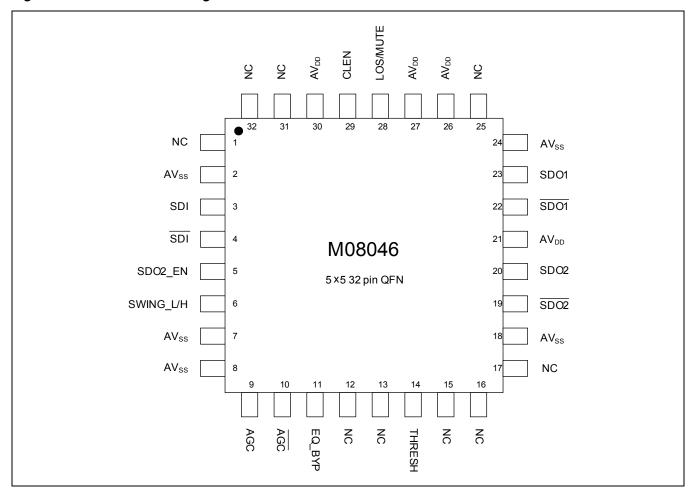

The pin assignment is illustrated in Figure 2-1. The M08046 package is RoHS compliant. This package is backwards compatible with the standard soldering techniques as defined in JEDEC-STD-020C (SnPb Process).

Figure 2-1. M08046 Pin Assignments

# 2.1 Pin Descriptions

Table 2-1. Power Pins

| Pin Name         | Pin Number      | Function        | Туре  |

|------------------|-----------------|-----------------|-------|

| AV <sub>SS</sub> | 2, 7, 8, 18, 24 | Ground          | Power |

| AV <sub>DD</sub> | 21, 26, 27, 30  | Positive Supply | Power |

### Table 2-2. High-speed Signal Pins

| Pin Name                           | Pin Number | Function                                                                | Туре       |

|------------------------------------|------------|-------------------------------------------------------------------------|------------|

| SDI/SDI 3, 4 Non-inverting and Inv |            | Non-inverting and Inverting Serial Data Input to the adaptive equalizer | CML input  |

| SD01/SD01                          | 22, 23     | Non-inverting and Inverting Differential Serial Data Output             | CML output |

| SD02/SD02                          | 19, 20     | Non-inverting and Inverting Differential Serial Data Output             | CML output |

Table 2-3. Control/Interface Pins

| Pin Name            | Pin Number                                                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Default            | Type         |

|---------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|

| NC                  | 1                                                                                               | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N/A                | N/A          |

| SDO2_EN             | SD02_EN 5 Enable Input for SD02 Outputs:  Low = SD02 output disabled High = SD02 output enabled |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Internal pull down | CMOS input   |

| SWING_L/H 6         |                                                                                                 | Enable Input for High Swing Output on SD01/2:  Low = 750 mV <sub>PP</sub> diff. (default)  High = 1050 mV <sub>PP</sub> diff.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Internal pull down | CMOS input   |

| AGC/ <del>AGC</del> | 9, 10                                                                                           | External AGC (Automatic Gain Control) capacitor connection points.<br>Use 1.0 µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Internal pull up   | Analog input |

| EQ_BYP 11           |                                                                                                 | Input control signal that when enabled (High) bypasses the inputs directly to the output stage.  Low = Normal operation  High = Disables EQ and bypasses input to output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Internal pull down | CMOS input   |

| NC                  | 12, 13                                                                                          | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N/A                | N/A          |

| THRESH 14           |                                                                                                 | Input control signal voltage. Programmable cable length forced mute threshold. This function is disabled if <b>LOS/MUTE</b> = Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Internal pull down | Analog input |

| NC                  | 15, 16, 17, 25                                                                                  | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N/A                | N/A          |

| LOS/MUTE            | 28                                                                                              | Bidirectional signal that can be used as an input control signal or as an output status indicator.  When configured as an input by forcing a voltage on LOS/MUTE = High, the SDO outputs will be inhibited at logic low (outputs muted). See Table 1-4 for CMOS input levels.  When LOS/MUTE = Low (V <sub>SS</sub> ), the output is never muted and the programmable cable length based mute function is disabled.  When configured as an output (tied to a high-impedance input) or left floating, the programmable inhibit based on cable length is enabled. See Table 1-8 for LOS/MUTE pin output levels.  Configured as Output:  Low = Input signal detect  High = Loss of signal  Configured as Input:  Low = Never mute  High = Force Mute | _                  | CMOS input   |

| CLEN                | 29                                                                                              | Cable length Indicator output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                  | Analog outpu |

| NC                  | 31, 32                                                                                          | Do not connect to the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N/A                | N/A          |

NOTE:

Internal pull-up/pull-down is 100 k $\Omega$ .

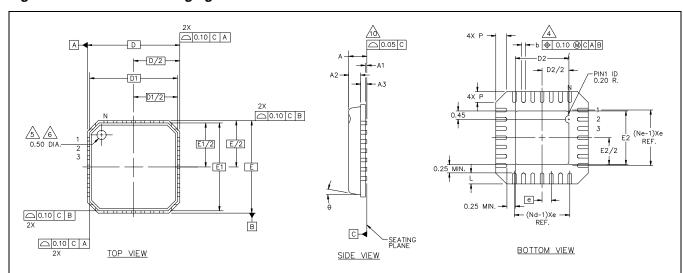

# 2.2 Package Drawing

The package for the M08046 is illustrated in Figure 2-2 below.

Figure 2-2. M08046 Packaging Details—Amkor

Note: View is for a 28 pin package. All dimensions in the tables apply for the 32 pin package

| S<br>Y | PITCH | VARIAT   | ION D | N <sub>0_</sub> |  |

|--------|-------|----------|-------|-----------------|--|

| м в О  |       |          |       |                 |  |

| L      | MIN.  | NOM.     | MAX.  | 'E              |  |

| е      |       | 0.50 BSC |       |                 |  |

| Ν      | 32    |          |       |                 |  |

| Nd     |       | 8        |       |                 |  |

| Ne     |       | 8        |       |                 |  |

| L      | 0.30  | 0.40     | 0.50  |                 |  |

| р      | 0.18  | 0.23     | 0.30  | 4               |  |

| Q      | 0.00  | 0.20     | 0.45  |                 |  |

| D2     | 3.15  | 3.30     | 3.45  |                 |  |

| E2     | 3.15  | 3.30     | 3.45  |                 |  |

|        |       |          |       |                 |  |

| S            |            | COMMON               | 1    |    |  |

|--------------|------------|----------------------|------|----|--|

| S<br>Y M B O | DIMENSIONS |                      |      | No |  |

| ို           | MIN.       | NOM.                 | MAX. | Т, |  |

| Α            | -          | 0.85                 | 0.90 |    |  |

| Α1           | 0.00       | 0.01                 | 0.05 | 11 |  |

| Α2           | -          | 0.65                 | 0.70 |    |  |

| А3           |            | 0.20 REF.            |      |    |  |

| D            |            | 5.00 BSC             |      |    |  |

| D1           |            | 4.75 BSC<br>5.00 BSC |      |    |  |

| Ε            |            |                      |      |    |  |

| E1           | 4.75 BSC   |                      |      |    |  |

| θ            |            |                      | 12°  |    |  |

| Ρ            | 0.24       | 0.42                 | 0.60 |    |  |

| R            | 0.13       | 0.17                 | 0.23 |    |  |

|              |            |                      |      |    |  |

NOTES:

2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. - 1994.

3. N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

A. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED

BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

7. ALL DIMENSIONS ARE IN MILLIMETERS.

8. THE SHAPE SHOWN ON FOUR CORNERS ARE NOT ACTUAL I/O.

9. PACKAGE WARPAGE MAX 0.05mm.

APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDING PART OF EXPOSED

PAD FROM MEASURING.

11. APPLIED ONLY FOR TERMINALS.

Please see Amkor's Application Note for PCB footprint (referenced in the Section A.2.1).

# 2.3 Manufactureability

The values shown in this section may change; however, these are standard requirements.

### 2.3.1 Electrostatic Discharge

Tested per JESD22-A114. This device passes 2000 V of ESD Human Body Model (HBM) testing. Tested per JESD22-C101. This device passes 500 V of ESD Charged Device Model (CDM) testing. Tested per EIA/JESD78. This device passes 150 mA of trigger current at 85 °C during Latchup testing.

### 2.3.2 Peak Reflow Temperature

M08046G (RoHS compliant package): Peak reflow temperature is 260 °C per JEDEC standards.

### 2.3.3 Moisture Sensitivity Level (MSL)

All versions of this device (Std Pb-type and RoHS compliant packages) are Moisture Sensitivity Level (MSL) 3 per J-STD-020B and J-STD-033.

# 3.0 Functional Description

### 3.1 Pin Descriptions

### 3.1.1 General Nomenclature

Throughout this data sheet, physical pins will be denoted in **BOLD** print. An array of pins can be called by each individual pin name (e.g. **MF0**, **MF1**, **MF2**, **MF3**, and **MF6**) or as an array (e.g. **MF[3...0**, 6] or **MF[3:0**, 6]).

### 3.1.2 High-Speed Input

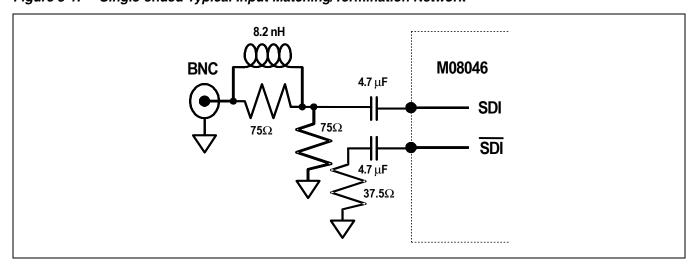

Digital video coaxial cables are AC-coupled to the high-speed low-noise inputs **SDI/SDI**, which are designed to operate in both single-ended and differential modes. The typical application is single-ended into the non-inverting **SDI** input with the inverting **SDI** input biased to match the bias on the input used.

The M08046 does not contain any internal input terminations and requires both external input termination as well as the matching circuit to improve input return loss. The package and IC design of the M08046 have been optimized for high-speed performance, allowing it to have typical return loss values of 13 dB at 3 GHz and 30 dB at 1.485 GHz, using the recommended external matching/termination network and commonly employed right-angle, through-hole, or vertical mount 75  $\Omega$  BNC connectors. For a non-inverting single-ended operation, the recommended input circuit is shown in Figure 3-1. For a differential operation, the matching/termination circuit on SDI should be duplicated on  $\overline{\text{SDI}}$ . The internal pull ups automatically bias  $\overline{\text{SDI/SDI}}$  for proper AC coupled operations.

Figure 3-1. Single-ended Typical Input Matching/Termination Network

### 3.1.3 High-Speed Outputs

The high-speed CML differential outputs after equalization are made available on the SDO1, SDO1, SDO2, SDO2 pins. By default only the SDO1/SDO1 outputs are enabled, SDO2/SDO2 are enabled when SDO2\_EN = High. Two swing levels are available; 750 mV<sub>PP</sub> and 1050 mV<sub>PP</sub> when SWING\_L/H = High, the 1050 mV output mode is selected, when SDO2\_EN = High, this affects both SDO1 and SDO2.

### 3.1.4 Adaptive Equalization Selection

In a typical operation, the adaptive equalization is enabled with **EQ\_BYP** = Low; however, with **EQ\_BYP** = High, the adaptive equalization and DC restore circuit is bypassed and the input is fed directly to the output.

### 3.1.5 Cable Length Indicator

When adaptive equalization is enabled (EQ\_BYP = Low), an analog voltage inversely proportional to the cable length is made available on **CLEN**. The same transfer function applies to all bit rates. When adaptive equalization is disabled (EQ\_BYP = High), the **CLEN** voltage goes to its highest value (this indicates 0 m cable length). During an LOS (Loss Of input Signal) event, the voltage falls to its lowest value.

### 3.1.6 Output Mute and Signal Detect

LOS/MUTE is a bi-directional pin that acts as an LOS detect output or a MUTE input.

When a voltage is forced on the pin, **LOS/MUTE** is a MUTE input. With **LOS/MUTE** = High ( $V_{DD}$ ), the outputs of the M08046 will be inhibited at logic low. When **LOS/MUTE** = Low ( $V_{SS}$ ), the output is never muted and the programmable cable length based mute function is disabled.

When the pin is tied to a high impedance node or left floating, **LOS/MUTE** is an LOS indicator output. In the event of an LOS, the output is muted. The inhibit threshold is set with an analog voltage applied to the THRESH input pin. This threshold will depend on cable type (e.g. Belden 1694A or 8281). To achieve maximum cable length equalization, the THRESH pin should be left open. Decoupling capacitors should be used between the THRESH pin and GND.

### 3.1.7 Equalizer Detailed Description

The basic equalizer design consists of interlaced stages of gain and equalization to maximize both the overall equalization gain as well as the input sensitivity for maximum performance with minimum jitter. In order to achieve maximum distance at 270 Mbps, 1485 Mbps and 2970 Mbps with Belden 1694A, the overall equalizer block has over 50 dB of broadband signal boost and maintains an input sensitivity of approximately 10 mV.

Since signals are launched with different rise and fall times which can vary substantially (especially at the receive end after going though a wide dynamic range of valid cable lengths) the equalization routine determines both the bit rate and the resultant signal HF attenuation as opposed to just looking at the launch edge rates. By determining both sets of conditions, it is possible to optimize the equalizer for the different rates. For example, the M08046 maintains the same maximum cable length as optimized SD-only equalizers. An SD signal through a short cable can have the same edge rate as an HD signal through a long cable; yet, both conditions require different levels of equalization as well as different optimized inverse-transfer functions. The advanced equalization technology can make the distinction between the two cases for optimal performance. This also leads to proper mute threshold (THRESH) and cable length indicator (CLEN) operation that is independent of the bit rate.

In order to accommodate both the worst case equalizer pathological patterns as well as some customer derived worst case DC offset patterns, a high-gain slicer is included in the signal path to correct for any eye-crossing

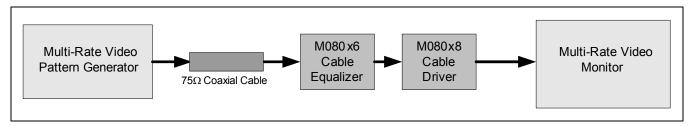

wander due to AC coupling of the input. Figure 3-2 shows the test set used by Mindspeed to evaluate the performance of the M08046.

Figure 3-2. Test Setup Diagram for Cable Equalizer Evaluation

# **Appendix**

# A.1 Glossary of Terms/Acronyms

BER Bit Error Rate

CD Cable Driver

CDA Cable Distribution Amplifier

CML Current Mode Logic

DDI Differential Data Inputs

EMI Electro Magnetic Interference

EQ Equalizer or Equalization

ESD Electro Static Discharge

GREEN Environmentally friendly

HD High Definition

HW Hardware ID Identifier

I/O Input/Output

QFN Quad Flat No Lead

RoHS Restriction of Hazardous Substances

SD Standard Definition

SDI Serial Digital Input

SDO Serial Digital Output

SE Single Ended

SW Software

### A.2 Reference Documents

### A.2.1 External

The following external documents were referenced in this data sheet.

- Application Notes for Surface Mount Assembly of Amkor's QuadFlatNoLead (QFN) Packages

- Amkor Technology Thermal Test Report TT-00-06 (See http://www.amkor.com for detailed information)

#### www.mindspeed.com

General Information: Telephone: (949) 579-3000 Headquarters - Newport Beach 4000 MacArthur Blvd., East Tower Newport Beach, CA 92660

© 2011 Mindspeed Technologies<sup>®</sup>. Inc. All rights reserved.

Information in this document is provided in connection with Mindspeed Technologies<sup>®</sup> ("Mindspeed<sup>®</sup>") products. These materials are provided by Mindspeed as a service to its customers and may be used for informational purposes only. Except as provided in Mindspeed's Terms and Conditions of Sale for such products or in any separate agreement related to this document, Mindspeed assumes no liability whatsoever. Mindspeed assumes no responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any damages resulting from such improper use or sale.